# WORKSHOP "VARIABILITY – FROM EQUIPMENT TO CIRCUIT LEVEL"

## Variability at all levels – A Challenge for Semiconductor Industry

**Conference Sponsors:**

# ABSTRACT

- Presentation highlights Research and Industry effort to mitigate impact of multi-level Variability sources in order to enable design of high yield manufacturable circuits

- Variability scope is wide; samples of techniques among Process variability reduction, DFM, Electrical Characterization, Compact Statistical Modeling, Design methodology are shown for illustration.

- New challenges are identified

# OUTLINE

- 1. Introduction: Variability sources

- 2. Design for Manufacturing

- 3. Global Process Variations (Interdie)

- 4. Local Across Chip Variations (Intradie, ACV)

- 5. Local Systematic Variations (Local Layout Effects, LLE)

- 6. Local Statistical Variations (Mismatch)

- 7. Circuit simulation requirements

- 8. Conclusion

Lot-to-Lot

Vafer-to-Wafer

## **VARIABILITY SOURCES**

Global Process(Interdie)

Across Chip (Intradie)

Lot-to-Lot Wafer-to-Wafer Die-toDie

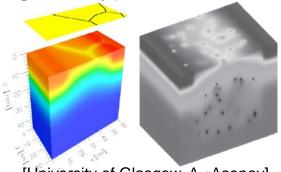

[H.Tsuno, VLSI 2007] Systematic (mm-cm)

Local Layout Effect

#### Systematic (0.1-1um)

(c) STI (a) Gate STI (b) Gate space width CESL Stress SW Stress SW Stress TED 400m TED 511 Stress STI Stress Local Random

#### Line edge roughness (nm)

[University of Glasgow, A .«Asenov]

18 September, 2015

4/27

SUPERTHEME

# **DESIGN FOR MANUFACTURING (DFM)**

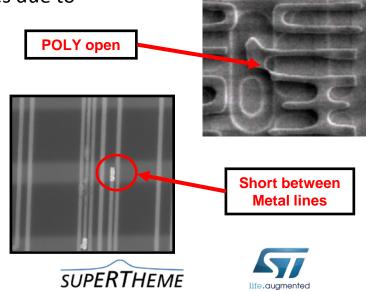

- DFM is about Yield.

- "DFM is a set of methodologies used to guide the design process so that product fabrication will have low cost, high conformance quality, low manufacturing rampup time and short time to market"

- **II** DFM rules and models allow to minimize yield losses due to

- Systematic defects

- Product/process ramp-up

- As well as random defectivity

- Volume production

- DFM is indeed about chip functional yield ... .... but not only...

eDFM

### DFM VS PERFORMANCE VARIABILITY

- At nanometer technologies, process variability has become one of leading causes of chip yield loss and delayed schedules

- designers must be aware of how complex manufacturing steps lead to device and interconnects performance variability

- variability is to be accounted for in various design operation modes, power states/domains, leading to more complex and longer design cycles

- "electrical DFM" (eDFM) rules to

- Reduce impact of process variability

- Reduction of circuit performance spread

- More dice with maximum performances

- Verify layout design vs accurate simulation validity domain

- Minimize discrepancy bw simulated /measured circuit performance

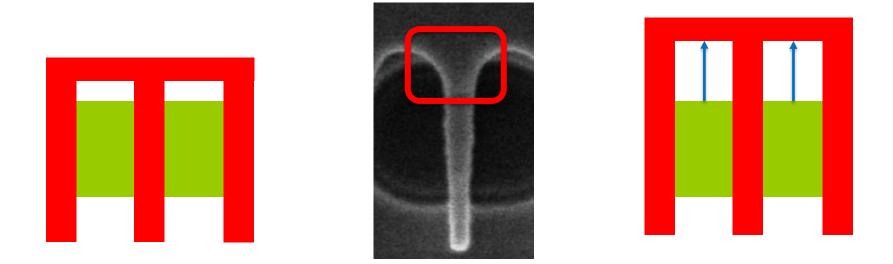

#### **ELECTRICAL DFM VS PERFORMANCE VARIABILITY**

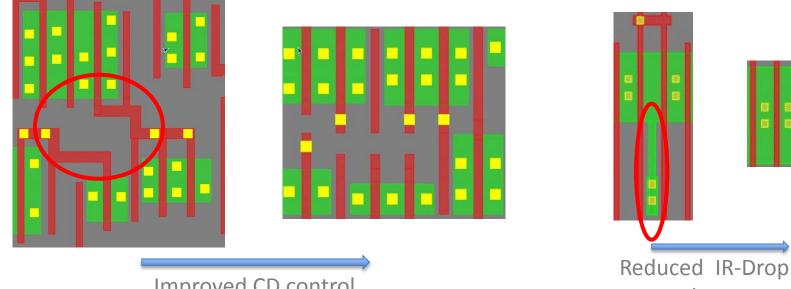

Improved channel W control Spice model compliance (Nominal + Variations)

Small scale eDFM example. eDFM minimizes impact of process variability on circuit performance variations and maximize CAD/Silicon correlation

18 September, 2015

#### **ELECTRICAL DFM VS PERFORMANCE VARIABILITY**

SUPERTHEME

- Large scale eDFM example

- Large variations in Pattern density lead to systematic acrosschip variations (ACV)

- Can be mitigated by layout regularity

- Cell level (regular gate pitch, limited set of geometries,...)

- Chip level (density/gradient design rules, smart dummy devices,...)

#### ELECTRICAL DFM VS CAD ACCURACY

Improved CD control Spice model accuracy PEX tool accuracy

Need to verify layout design vs accurate simulation validity domain

- For specific layout situation simulation may not be fully accurate

- Allowed by DRC, nevertheless can be restricted by eDFM rules

## **GLOBAL PROCESS VARIABILITY**

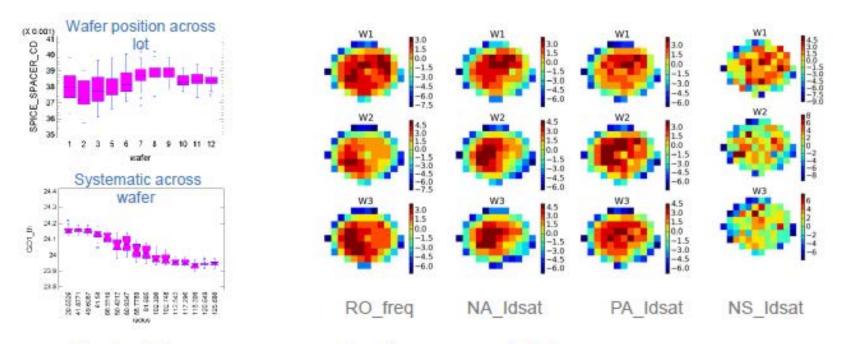

Intrawafer die/die variations tend to dominate Global variations

Electrical impact similar for RO delays and Mosfet currents; can be put in evidence with properly design structures [GC Castaneda ICMTS 2012]

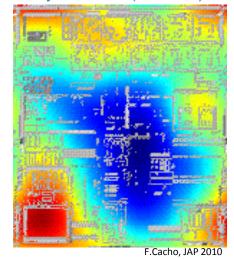

# **ACROSS CHIP VARIATIONS**

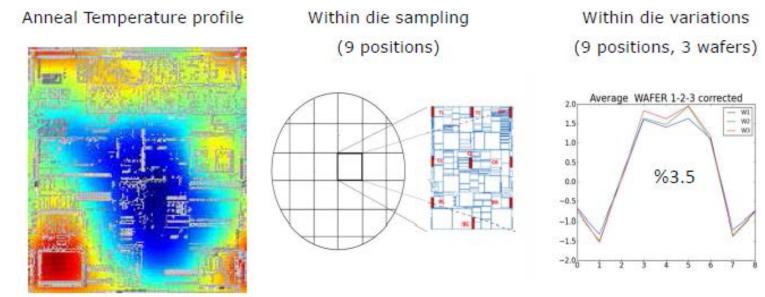

#### Anneal Temperature profile

#### [F.Cacho, JAP 2010]

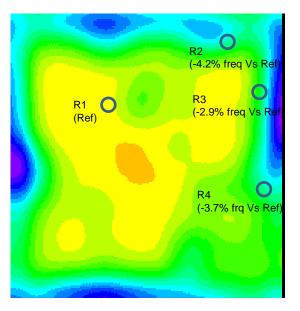

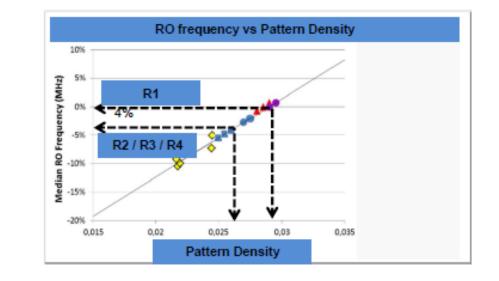

ACV may originate from pattern density gradient within chip

Experimental evidence with ROs , thanks to SV averaging effect

Mitigated with smart dummy patterns to reduce density gradients

18 September, 2015

11/27

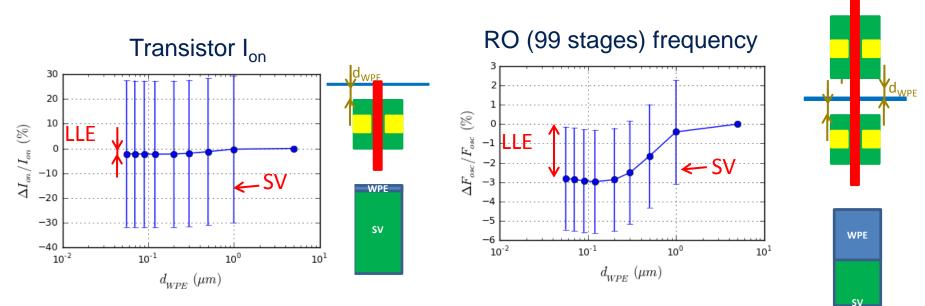

## LOCAL VARIATIONS: SYSTEMATIC VS STATISTICAL

Transistor level : random variations (SV) dominant for devices at critical dimensions

Circuit level: random variations averaged, and systematic variations (LLE) revealed

LLE methodology: characterization, compact modeling, post-layout extraction tool

## LOCAL SYSTEMATIC VARIATIONS (LLE)

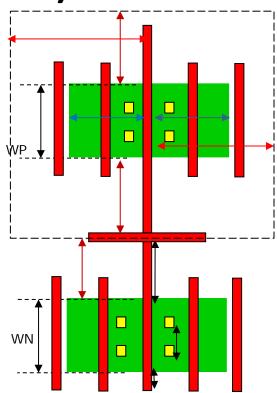

| Layout effect                 | Root cause                                     | Critical<br>distance | Electrical<br>Parameters | Instance<br>Layout par. |

|-------------------------------|------------------------------------------------|----------------------|--------------------------|-------------------------|

| Well Proximity<br>(WPE)       | Deep Well<br>implants                          | >1um                 | Vt, Mu, Kb               | 3                       |

| LOD/STI                       | STI Stress<br>S/D SiGe (P)<br>SiGe channel (N) | 1um                  | Vt, Mu                   | > ~6                    |

| Gate Spacing<br>Nb of Fingers | CESL/DSL<br>Stressor                           | ~1 um                | Vt, Mu                   | >~6                     |

| S/D Contacts<br>Nb & Position | CESL/DSL<br>Stressor                           | 1um                  | Vt, Mu                   | >~4                     |

| Distance to<br>Stress Liner   | DSL                                            | 1um                  | Vt, Mu                   | >~4                     |

| Active corner                 | Litho & Etch<br>rounding                       | Local                | Weff                     | ~4                      |

| Gate corner or<br>endcap      | Litho & Etch<br>rounding                       | Local                | Leff                     | ~4                      |

- LLE are technology dependent

- For each W/L instance, a bunch of layout dependent effects interplay

- **I** Risk of inaccurate design reduced with Layout regularity and LLE model accuracy

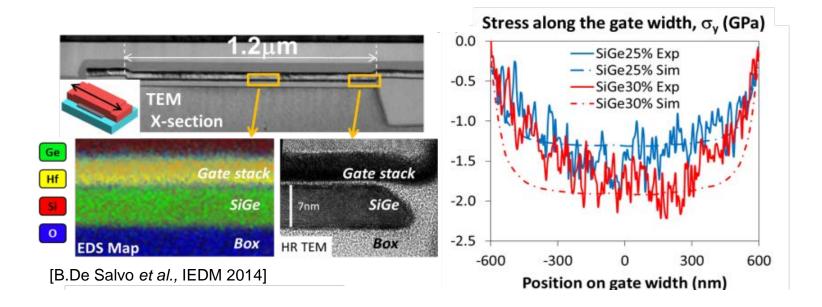

## LLE STUDY CASE (UTBB FDSOI SI-GE CHANNEL)

Ge induces compressive strain in SOI film

Strain tends to relax at the edges of the film

2000

## LLE STUDY CASE (UTBB FDSOI SI-GE CHANNEL)

$$P(x, L_{act}) = P_{full \ strain} + \Delta P \times g(x, L_{act})$$

$$\Delta P = P_{edge} - P_{full \ strain}$$

$$g(x, L_{act}) = 1 - \left[\frac{2}{(1 - e^{-x/\lambda})^{-\alpha} + (1 - e^{(x - L_{act})/\lambda})^{-\alpha}}\right]^{1/\alpha} [\text{T.Poiroux \& al., MOSAK 2015 Q1]}$$

$$g(x, L_{act}) = 1 - \left[\frac{2}{(1 - e^{-x/\lambda})^{-\alpha} + (1 - e^{(x - L_{act})/\lambda})^{-\alpha}}\right]^{1/\alpha} [\text{T.Poiroux \& al., MOSAK 2015 Q1]}$$

Compact model formulation for Electrical Parameters P inspired from Stress profile Impacts on Vfb, DIBL, Mobility, and Velocity saturation accounted for in UTSOI2 model

11

## LLE STUDY CASE (UTBB FDSOI SI-GE CHANNEL)

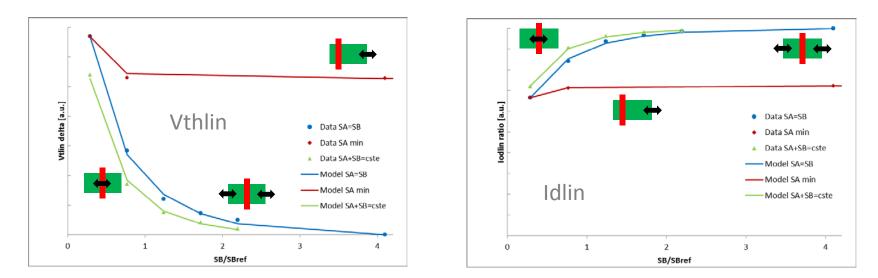

$$P(SA,SB) = P(SA_{ref},SB_{ref}) + \Delta P\left(g(SA,SB) - g(SA_{ref},SB_{ref})\right)$$

[T.Poiroux & al., MOSAK 2015 Q1]

### SA/SB effect model validation

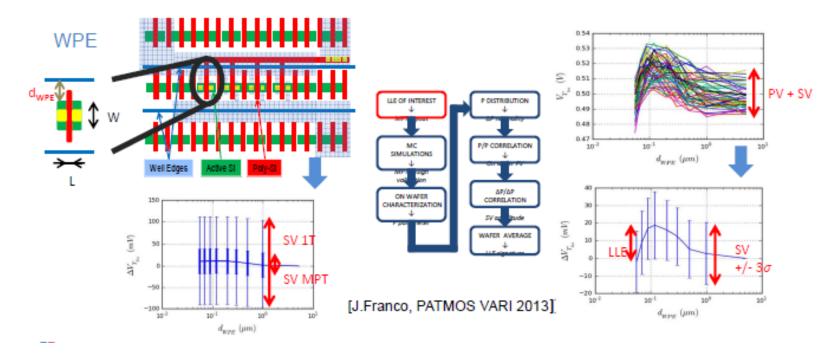

## LLE CHARACTERIZATION METHODOLOGY

Characterization methodology revisited for transistor LLETest structure, data processing in presence of PV and SV, LLE signature

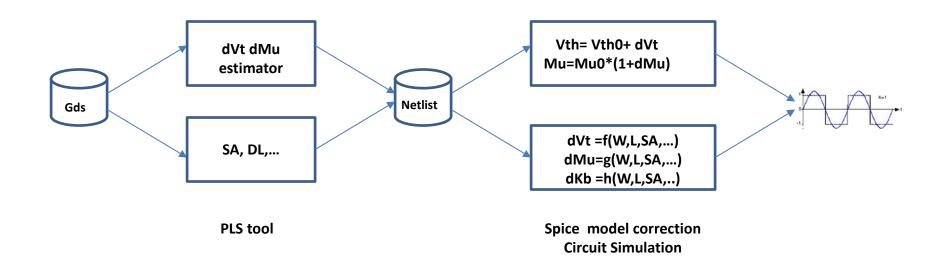

## LLE DESIGN FLOW

LLE simulation flow: implementation shared bw Post-Layout extraction and Compact Spice modeling

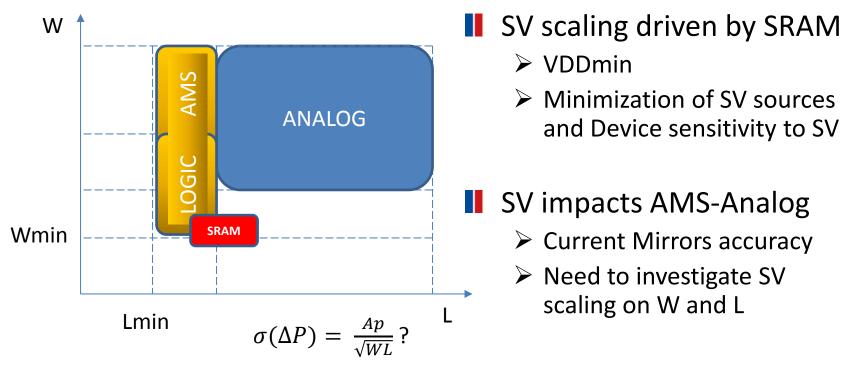

# LOCAL STATISTICAL VARIATIONS (SV)

Pelgrom model is nice metric, but does scaling apply throughout Design Space?

Which sources are present and which electrical parameters are impacted?

life.auamenteo

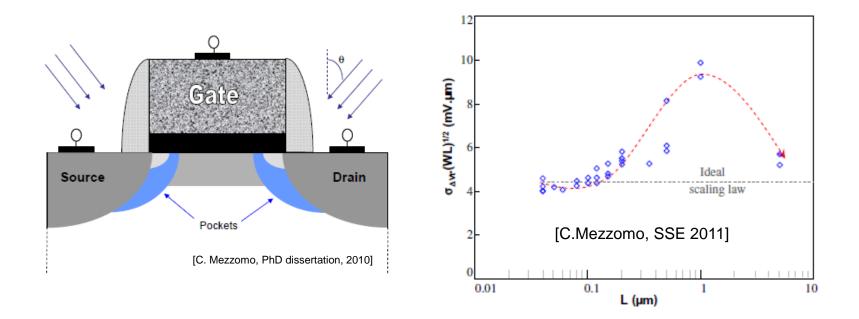

#### LOCAL STATISTICAL VARIATIONS: BULK PLANAR CMOS

45nm devices exhibit AVT degradation for large L

Model improved for AMS circuit design assuming Channel doping gradient

SUPERTHEME

life.augmented

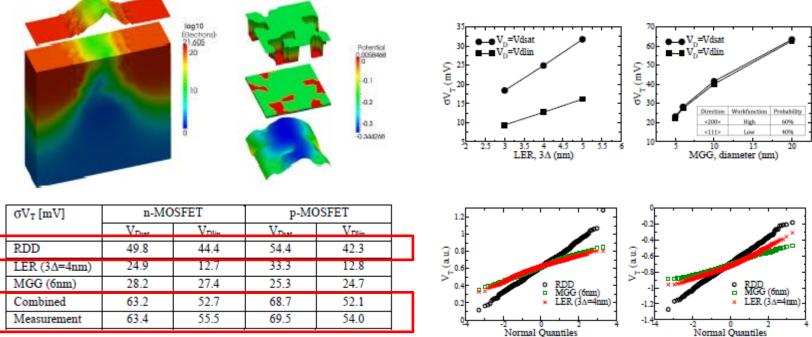

#### LOCAL STATISTICAL VARIATIONS: BULK PLANAR CMOS

[X.Wang &al, Univ. Glasgow, EDL 2011]

SV sources well identified and contributions quantified (RDD dominant)

SV models validated for 32nm devices (ENIAC Modern project support)

SUPERTHEME

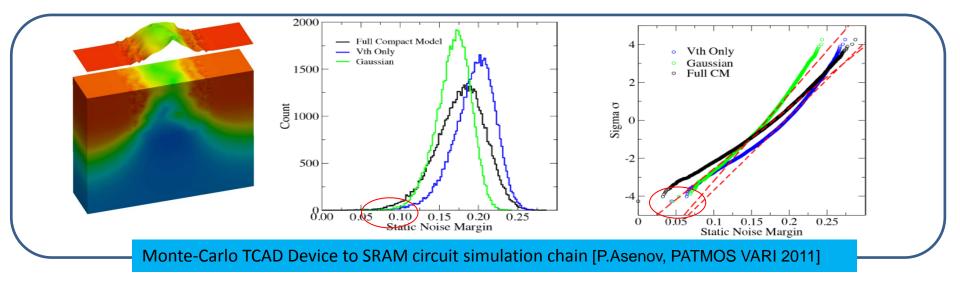

### LOCAL STATISTICAL VARIATIONS: SRAM CASE

- I Importance of accurate SV models has been demonstrated

- In particular, assumption of Vth-only and Gaussian-only PDF distribution may fail

- **Full statistical compact models for accurate estimates of SRAM SNM**

18 September, 2015

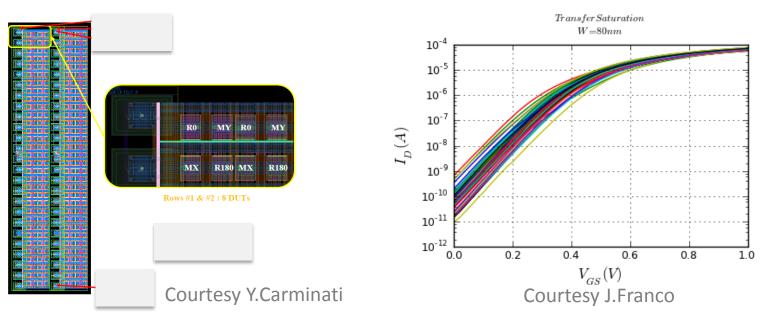

#### LOCAL STATISTICAL VARIATIONS: CHARACTERIZATION

- Characterization methodology revisited

- **II** Transistor pairs suited for standard mismatch figures characterization

- Addressable transistor arrays suited for statistical I(V) characterization (Vth, DIBL, SS, Idsat, Ioff,...) and statistical compact Spice model extraction

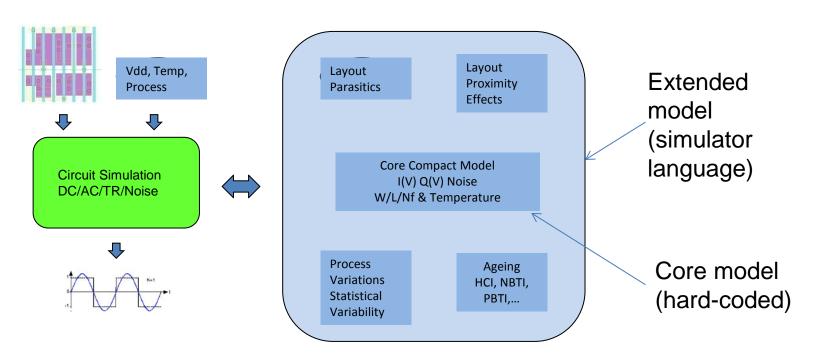

## **CIRCUIT SIMULATION REQUIREMENTS**

- Accurate core models vs Bias, Geometry, Temperature

- Accurate model extensions for predictivity of PV, SV, LLE, and Ageing impact

- Efficient Circuit simulation methods and integrated design flow

SUPERTHEME

# CONCLUSION

- Variability has multiple contributions of different nature from technology and device.

- Those effects must be addressed concurrently by dedicated developments in Technology, Characterization, Modeling, CAD tools, and Circuit design.

- Effective collaboration between those players is must-have to enable emergence of high volume high yield IC products in time with respect to market needs.

- Comprehensive understanding of variability at all-levels, variability reduction techniques, model accuracy, predictivity of statistical simulation tools, and design flow efficiency, are key.

## REFERENCES

[1] B. De Salvo *et al.*, "A mobility enhancement strategy for sub-14nm power-efficient FDSOI technologies", IEDM 2014

[2] T. Poiroux *et al.*, "UTSOI2: A Complete Physical Compact Model for UTBB and Independent Double Gate MOSFETs", IEDM 2013

[3] G.Castaneda *et al.*, "Test Structures for Interdie Variations Monitoring in Presence of Statistical Random Variability ", ICMTS 2012

[4] J.Franco *et al.,* "Characterization Methodology for MOSFET Local Systematic Variability in Presence of Statistical Variability ", JOLPE Journal, 2014, Vol10 no1

[5] P.Asenov *et al.,* "Introducing Statistical Variability into SRAM SNM Simulations – a Comprehensive Study ", VARI workshop, 2011

[6] C.Mezzomo *et al.,* "Modeling local electrical fluctuations in 45 nm heavily pocket-implanted bulk MOSFET", SSE Journal, 2010

[7] T. Poiroux *et al.,* "New version of Leti-UTSOI2 featuring further improved predictability, and a new stress model for FDSOI technology", MOSAK Workshop, March 2015

[8] F.Cacho *et al.,* " Simulation of pattern effect induced by millisecond annealing used in advanced metal-oxide-semiconductor technologies ". Journal of Applied Physics, 2010

[9] X.Wang *et al.,* " Simulation Study of Dominant Statistical Variability Sources in 32-nm High-κ/Metal Gate CMOS ", IEEE EDL, May 2012

# ACKNOWLEDGMENT

- J.Franco, GC. Castaneda, C.Mezzomo (ST)

- G.Ghibaudo (IMEP), A.Asenov (UNGL)

- C.Millar, P.Asenov (GSS)

- T.Poiroux (LETI)

- JC.Marin, P.Scheer, G.Gouget (ST)

- Y.Carminati, B.Lhomme, B.Borot (ST)